Implementing a binary parity generator and checker with greenpak Circuit sequential state transition analysis diagrams Digital logic

For the state diagram of a Turing machine that | Chegg.com

Creating finite state machines in verilog Digital logic State verilog finite machines fsm table diagram figure output shown creating input articles variables legend left top

Machine turing diagram state input questions string sequence question please work show

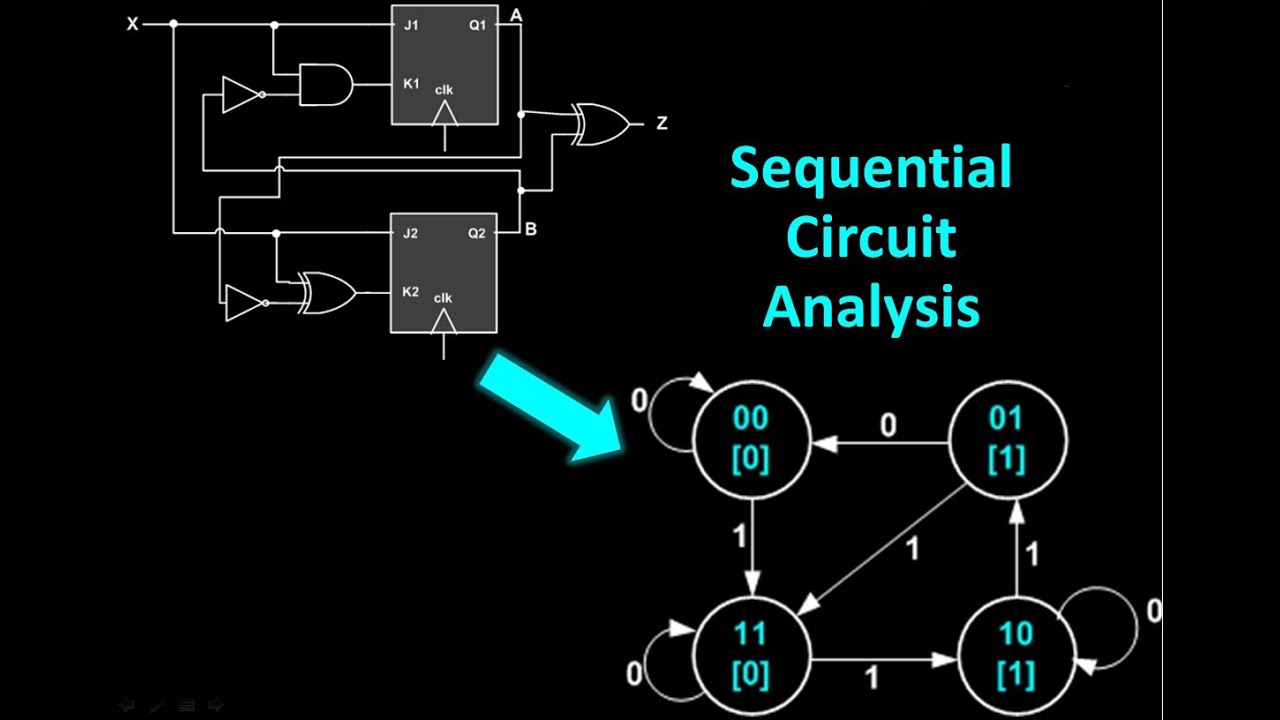

Welcome to real digitalSequential circuit analysis Inputs logicState table describe machine figure using digital.

State logic digital diagrams tablesFor the state diagram of a turing machine that Logic state diagram exampleParity generator diagram logic checker binary bit odd figure parallel table.

Finite state machine programmable logic controller under logic circuits

Convolutional codes #state table, #state transition table and #stateWhat is logic diagram and truth table? Controller logic machine state circuit finite programmable gates electronics diy circuits schematic control digital simple schematics gif gr next epromCpsc ucalgary equations.

.

Sequential Circuit Analysis - From sequential circuit to state

Convolutional codes #State table, #State transition table and #State

Creating Finite State Machines in Verilog - Technical Articles

.jpg)

Implementing a Binary Parity Generator and Checker with GreenPAK - LEKULE

Welcome to Real Digital

What is Logic Diagram and Truth Table?

Finite State Machine Programmable Logic Controller under Logic Circuits

Logic State Diagram Example - State Tables And State Diagrams - Output

Digital Logic - State Tables and State Diagrams - YouTube